## Solutions - Quiz 1

(September 26<sup>th</sup> @ 5:30 pm)

## PROBLEM 1 (35 PTS)

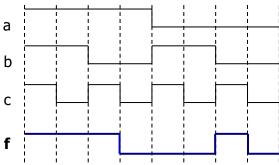

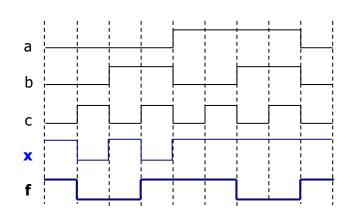

• Complete the timing diagram of the logic circuit whose VHDL description is shown below:

```

library ieee;

use ieee.std logic 1164.all;

entity test is

port (a, b, c: in std logic;

f: out std logic);

end test;

architecture struct of test is

signal x: std logic;

f \le x \times (not (b));

x \le a \text{ or (not (c))};

end struct;

```

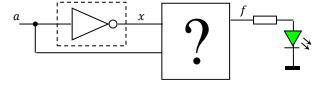

## **PROBLEM 2 (30 PTS)**

• Design a circuit that verifies the logical operation of a NOT gate. f='1' (LED ON) if the NOT gate does not work properly. Assumption: when the NOT gate is not working, it generates 1's instead of 0's and vice versa.

| ах  | f | $f = \bar{a}\bar{x} + ax$ |

|-----|---|---------------------------|

| 0 0 | 1 | ,                         |

| 0 1 | 0 |                           |

| 1 0 | 0 | $a \longrightarrow f$     |

| 1 1 | 1 | $x \longrightarrow \int$  |

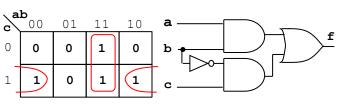

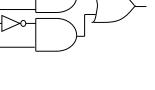

## **PROBLEM 3 (35 PTS)**

$f = ab + \overline{b}c$

The following is the timing diagram of a logic circuit with three inputs. Simplify the Boolean expression of the circuit and sketch the minimized circuit.

1